原文:Altera FPGA Architecture Whiter Paper.

这篇文章是Altera在2006年发布的FPGA架构白皮书,简单介绍了其当时的FPGA架构,包括LUT与ALM的设计、相比基本的LUT的优势、路由架构等内容。

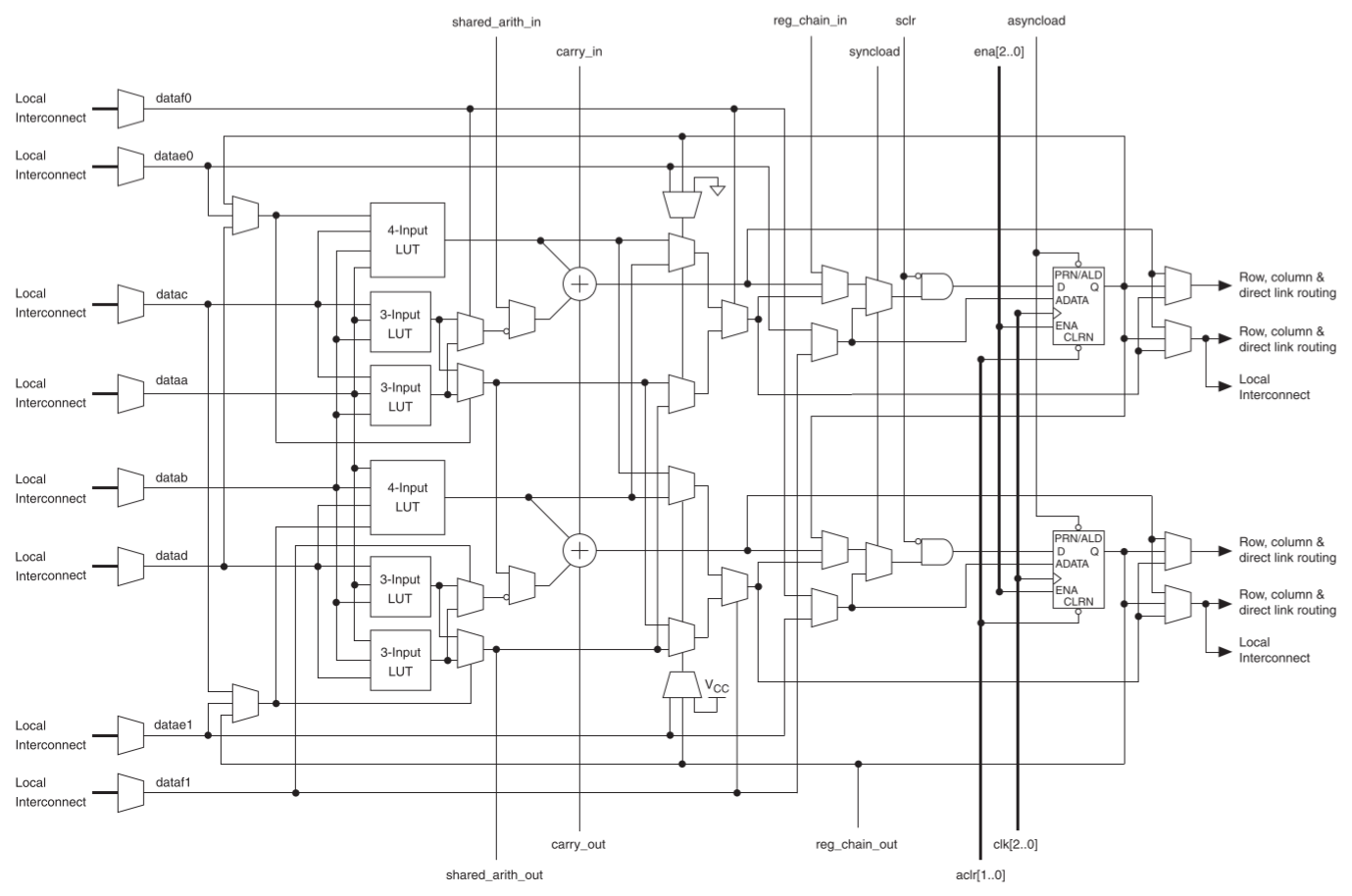

Logic Fabric

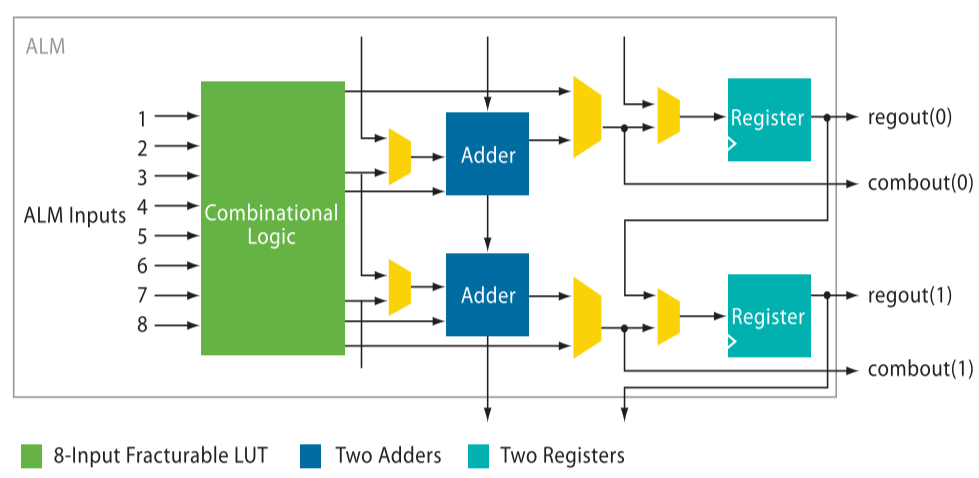

在Altear的FPGA器件上,一个最基本的模块是Adaptive Logic Module,即ALM,如上图所示。整个ALM由一个组合逻辑块、两个Adder、两个Register和一些其他连线组成,一个ALM可以实现一个完整的6输入LUT,或者两个独立的4输入LUT、一个5输入与一个3输入LUT、或其他更复杂的组合,两个LUT之间也可以共享输入,也可以实现7输入函数的一个子集,具体可以参考原文。

构建LUT

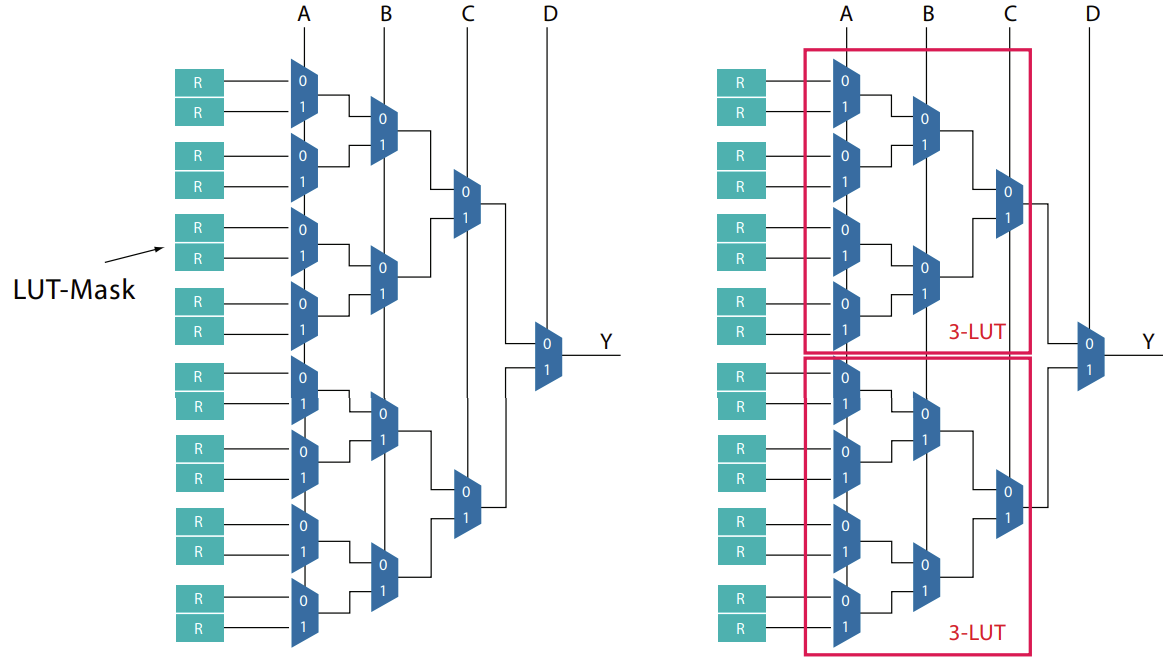

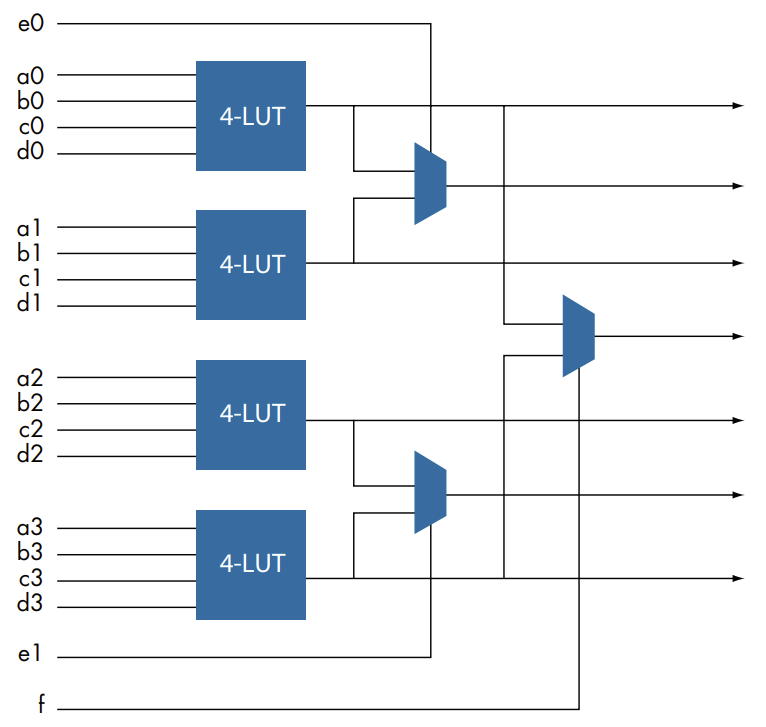

一个LUT由包含了configuratoin memory(CRAM)LUT-mask的SRAM以及一些负责选择CRAM输出的Mux组成,为了实现一个k输入LUT,我们需要2^k个SRAM位以及一个2^k输入的Mux,上图展示了一个4-LUT的结构,除了直接构建之外,也可以由两个3-LUT组合而成。同理,更大的LUT也可以由小LUT组合而成,如下图所示。

不过,我们仍然要注意上图中4-LUT和6-LUT的一些区别,若基本逻辑块的LUT大小不同,架构中LUT的数量、每个LUT可用的输入、通过LUT的延迟都会有所区别。即便6-LUT可以通过4个4-LUT实现,这种结构的效率是很低的,在上图中我们注意到,我们只用了16个输入线(应该是19?)中的6个,并产生了额外的延迟。不过并不是说直接构建6-LUT一定就好,我们也需要为6-LUT做出额外的优化。

设计ALM

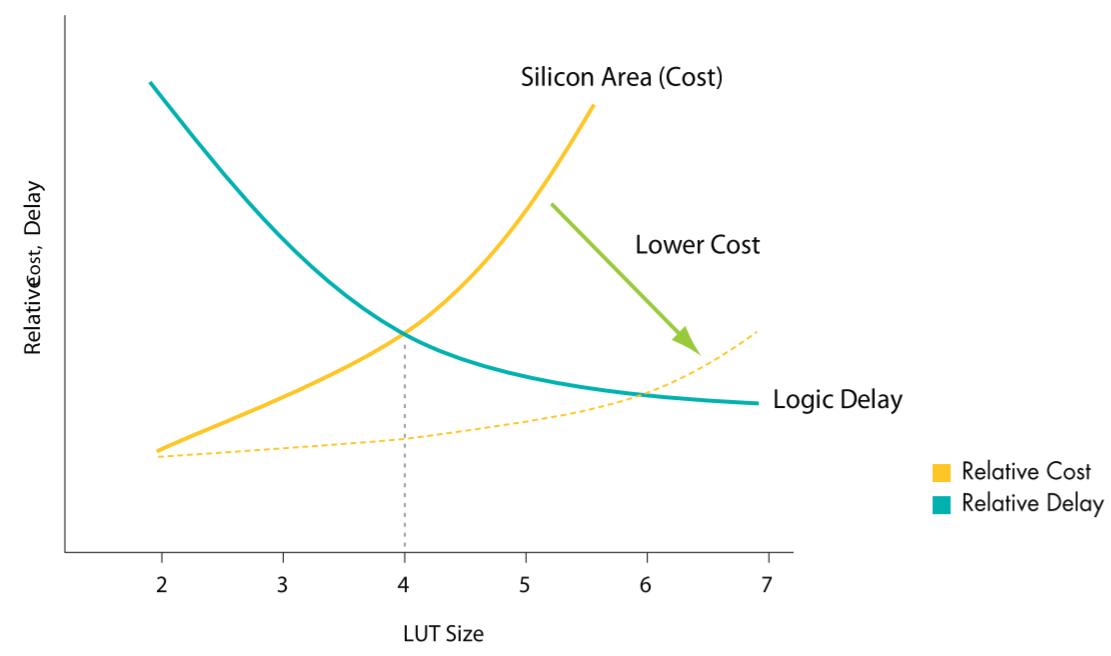

ALM的设计需要详细了解客户需求并研究各种架构的权衡,Altera的研究表明,6-LUT的设计可以缩短关键路径,提高14%的性能,但这种性能提升也会带来面积损失,由于更大的LUT设计和更多的LUT输入,面积增加了17%,下图说明了不同尺寸的LUT成本和延迟之间的权衡。设计ALM的基本思路是构建更大的LUT来提升性能,但也需要合理地划分为更小的LUT来避免面积增加,这种划分LUT的能力使其具有自适应性。

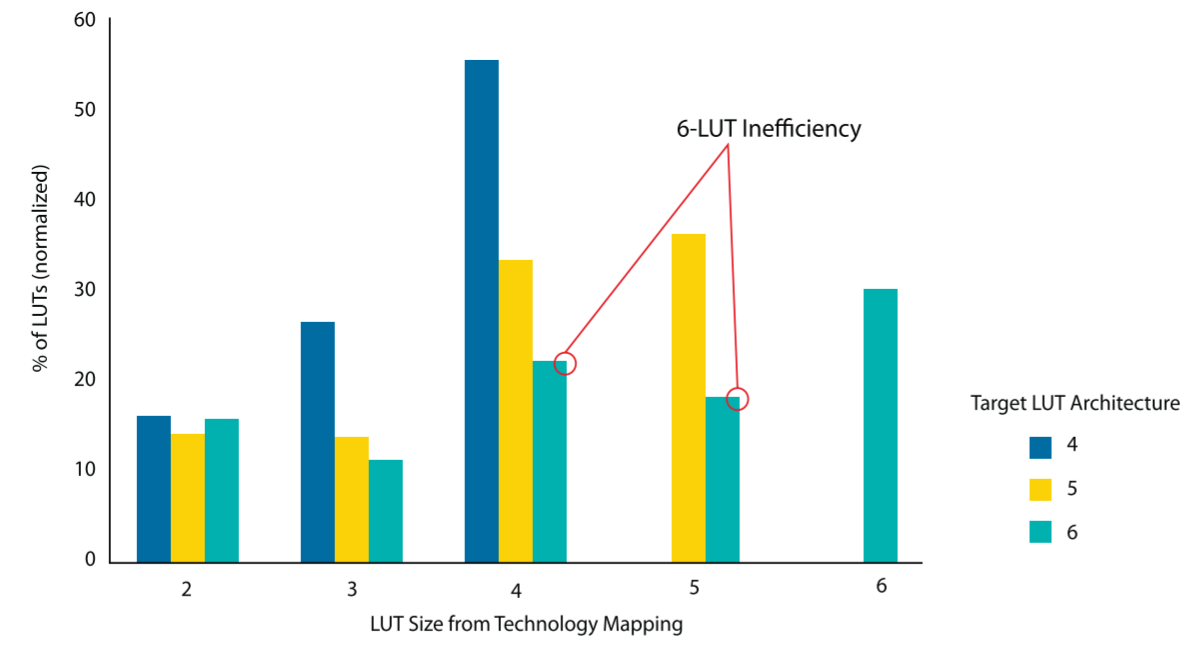

Altera对LUT与ALM的设计进行了复杂的建模,包括逻辑和存储器资源、架构的分层描述、FPGA时序与物理细节等。为了更好地理解使用6-LUT带来的面积损失,Altera分析了每个逻辑函数需要的输入数量,下图展示了目标为4-LUT、5-LUT和6-LUT架构时,综合过程中产生的LUT大小分布。我们注意到绝大多数函数不需要用到6-LUT,即使目标是6-LUT,但只有约30%的函数真正完整用到了6-LUT,除此之外,较小的函数在仅支持基本6-LUT的架构中无法有效实现,会浪费面积并增加成本,如果可以将6-LUT划分为更小的LUT,就可以在6-LUT中实现多个较小的功能,提高资源利用效率。

最终Altera的设计是ALM的8输入可拆分LUT,也就是之前ALM的图中展示的样子,下图详细展示了ALM的结构,说明了LUT-mask如何被拆分并在两个不同的逻辑块之间共享,Altera的FPGA综合、布局和布线结果显示,这种结构是最有成本效益的。

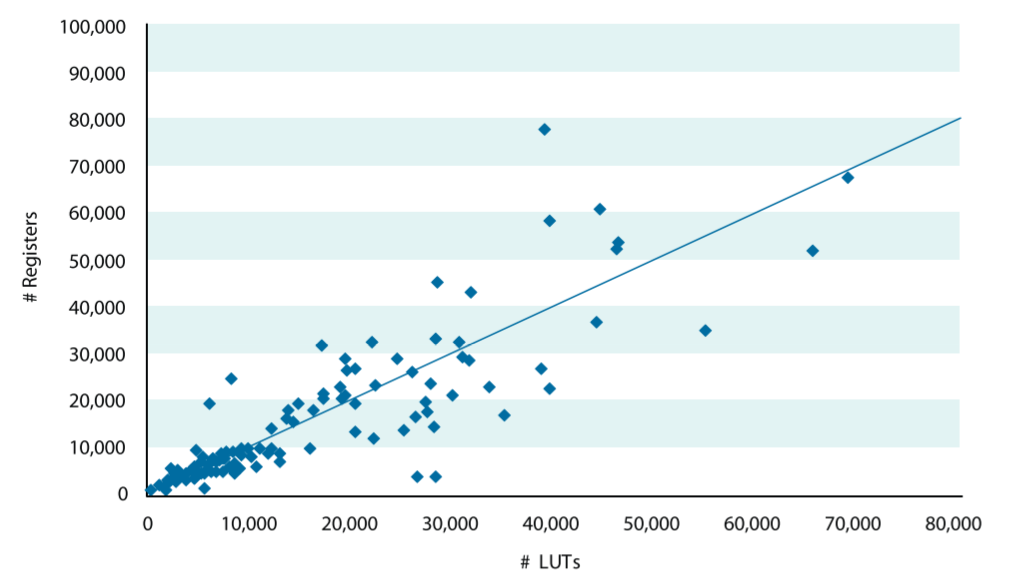

除此之外,ALM还包含了两个寄存器和两个加法器,添加寄存器是因为实验表明许多应用程序需要高于1:1的寄存器与LUT比值,下图中,几乎一半的设计中寄存器的数量比LUT更多。ALM还包含了加法器以增强ALM的算术计算能力,允许每个ALM进行两位的加法或一个三进制的加法。

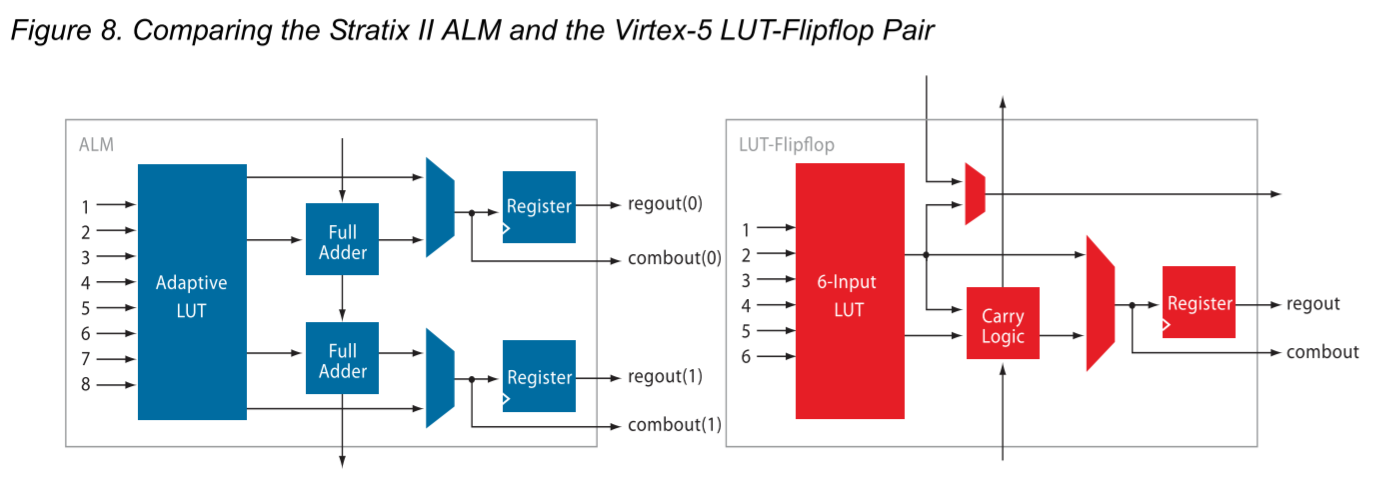

ALM的优势

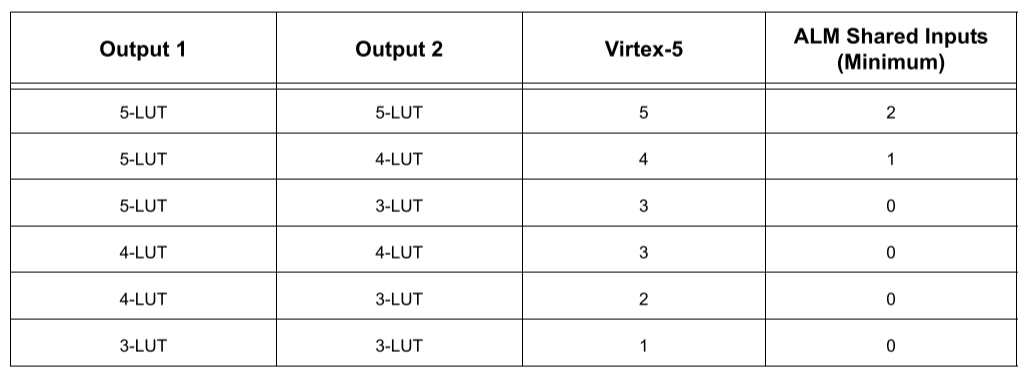

ALM相比基本的6-LUT效率更高,上图中,Virtex-5实现多个逻辑功能的能力有限,通常只能用作6-LUT,很难用作两个5-LUT,但ALM中的2个额外输入允许其用作两个完整的的5-LUT,提供显著的面积优势。下表中给出了一些功能组合需要的共享输入的数量,例如ALM可以实现2个独立的4输入函数,但Virtex-5 LUT需要3个共享输入。

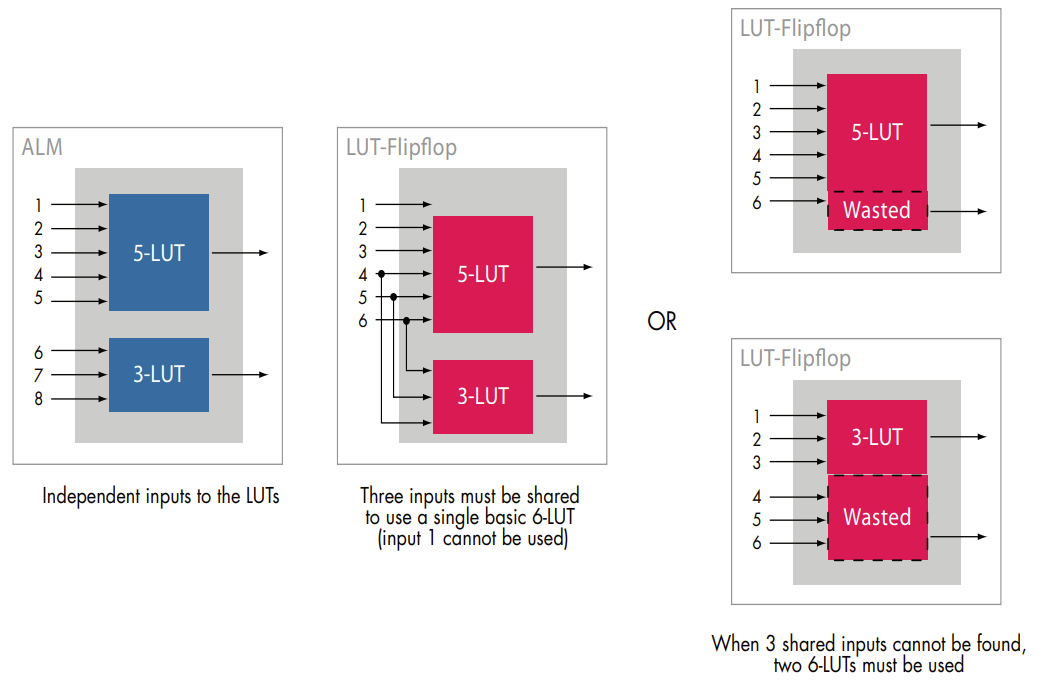

下图展示了另外一个例子,说明ALM可以再没有共享输入的情况下实现一个5输入函数和一个3输入函数,但Virtex-5的LUT需要3个共享输入。

路由架构

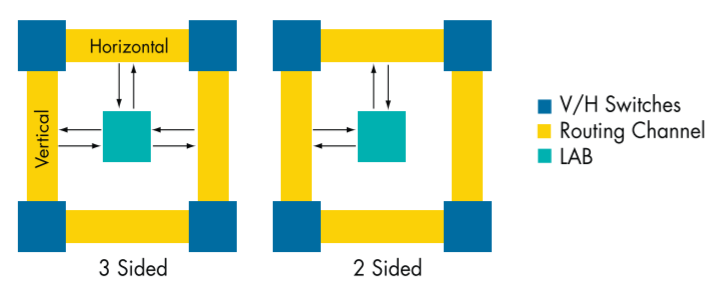

FPGA另一个关键特性是其路由架构,Stratix系列器件引入了MultiTrack互联,尽可能提升连接性能。路由架构提供不同逻辑块集群之间的连接,称为逻辑阵列块(logic array blocks,LAB),可以通过一个LAB到另一个LAB所需的跳数(hop)来衡量,跳数越少,模式越容易预测,性能越好,也越容易在CAD工具中优化。下图展示了Stratix中的路由架构,使用三边架构,通道包含了长度为4、8、16、24的导线,

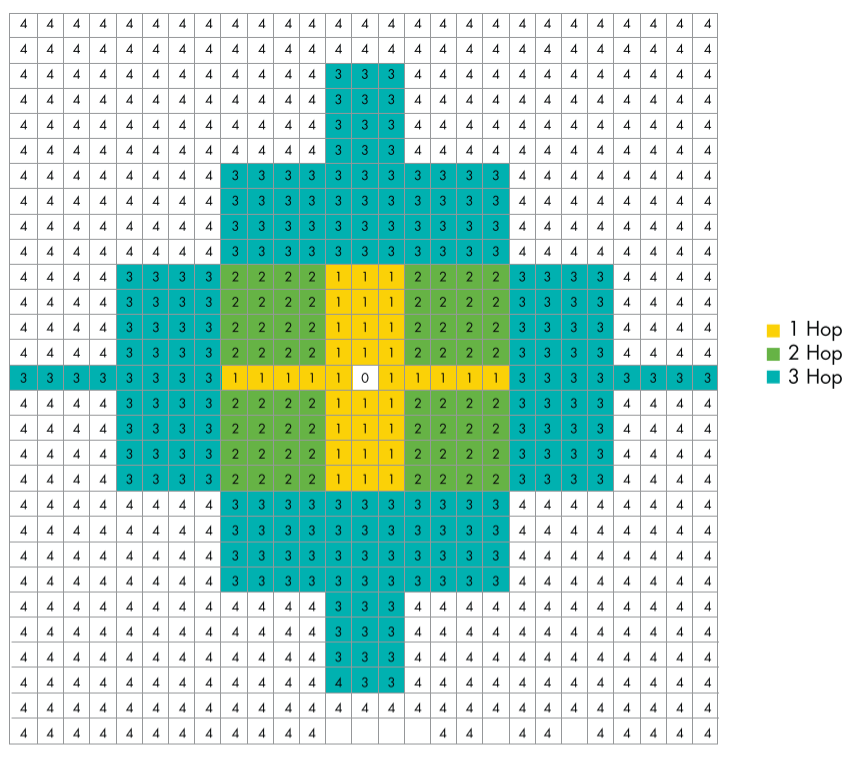

现在假设我们只考虑长度为4的线,下图展示了不同LAB连接到原点所在的LAB的跳数。