原文:Three Ages of FPGAs: A Retrospective on the First Thirty Years of FPGA Technology.

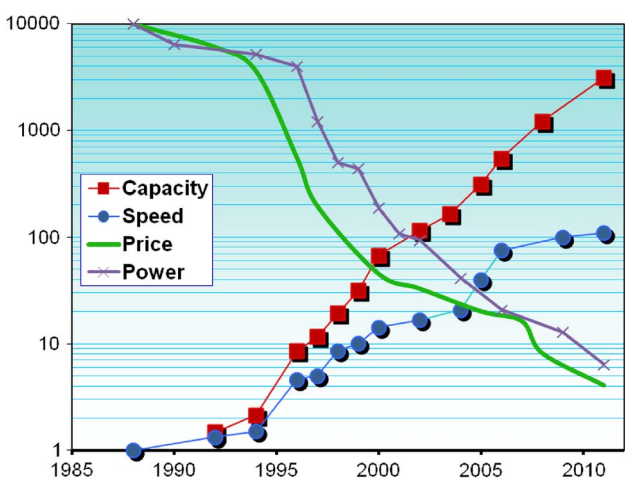

Xilinx在1984年首次推出第一款FPGA,在随后的30年中,FPGA容量增加了10000倍,速度提高了100倍,单位成本和能耗降低了1000倍,如下图所示。这种进步很大程度上是由工艺进步推动的,但不完全是。本文回顾了FPGA的三个时代,分别为:

发明时代 1984-1991

扩张时代 1992-1999

积累时代 2000-2007

FPGA与其他器件

FPGA与ASIC

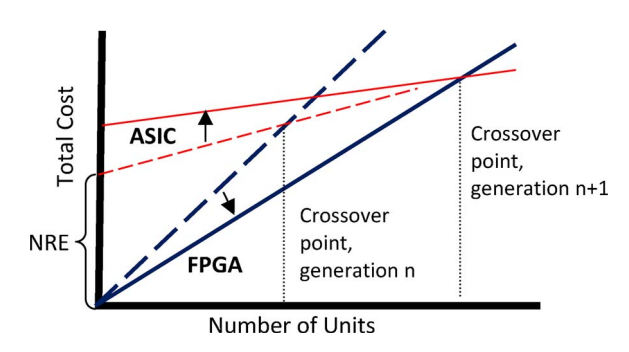

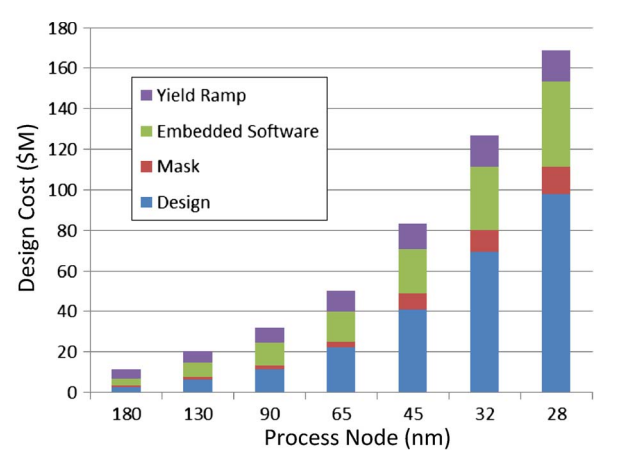

ASIC有所谓的Non-recurring Engineering即NRE成本,但FPGA没有,前期没有NRE成本保证了FPGA在一定数量上比ASIC成本更低,如下图所示。有趣的是,当工艺不断提升时,ASIC和FPGA都会受益,但两者的交叉点会往右移动,进一步增大FPGA的成本优势。这种特性推动FPGA不断满足ASIC的要求,不仅降低了前期成本,也降低了设计成本,包括设计、测试、信号完整性等方面的成本,且没有ASIC生产方面的风险。

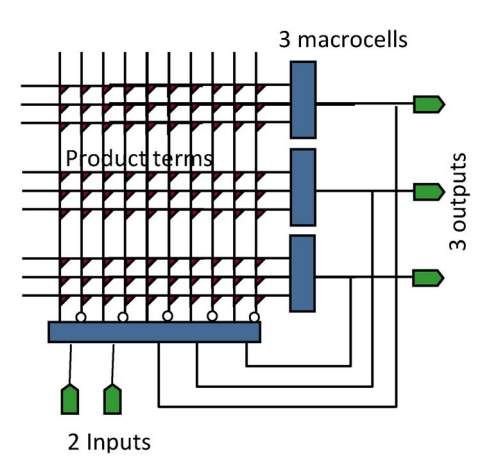

FPGA与PAL

FPGA并非第一种可编程逻辑器件,之前还有EPROM编程的可编程阵列逻辑(PAL),但FPGA有架构优势。为了理解这种优势,我们首先来看PAL的结构,如下图所示。PAL由两级逻辑结构组成,可以生成任意组合逻辑,从制造的角度来看,PAL和EPROM存储器阵列非常相似。

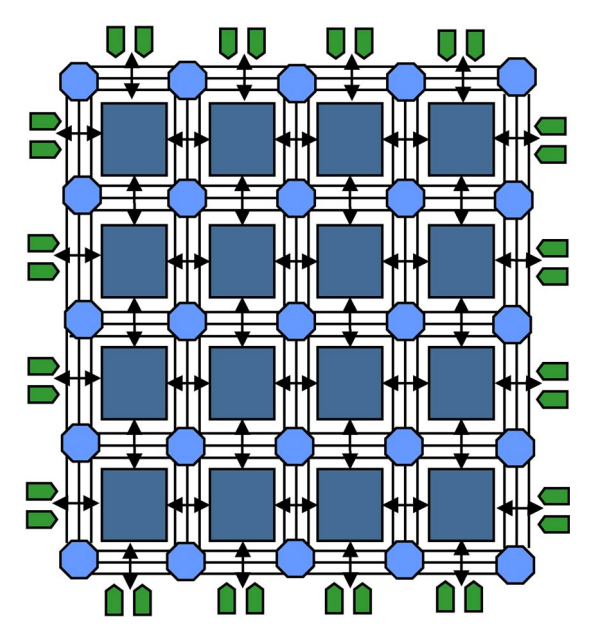

不过当考虑扩展时,PAL的架构问题很明显,因为阵列中可编程点的数量随着输入数量以平方增长,且延迟会增加,为保持速度,功耗也上升。Altera在1980年代推出了CPLD,由多个PAL模块组成,但FPGA则更有扩展性。FPGA的特点在于通过存储单元分布在阵列周围来控制功能和布线,架构如下图所示,可以很容易地提升容量和性能,不过也产生了一些附加的影响,如FPGA架构和内存有很大不同、逻辑单元更小、性能取决于布局和布线的结果、需要复杂的EDA软件等。

发明时代 1984-1991

第一个FPGA,Xilinx XC2064,仅包含64个逻辑块,每个逻辑块包含两个三输入LUT和一个寄存器。尽管容量很小,但却是一个非常大的芯片,比当时的商用微处理器还大。在早期,成本控制对FPGA的成功至关重要,比如芯片尺寸增加5%可能会使成本翻倍,甚至直接将良率降为0。同时,在1980年代,Xilinx基于LUT的四输入架构被认为是粗粒度的,许多LUT配置未被使用,或者有未使用的输入,浪费了空间,因而也有其他公司设计了包含固定功能的、更细粒度的架构。

在这一时代FPGA规模很小,并不会考虑自动布局布线,且当时个人计算机计算能力有限,ASIC布局布线都是在大型计算机上完成的,相比之下FPGA的布局布线通常都需要手工完成。完全不同的FPGA架构的结果是,FPGA供应商需要开发自己的EDA工具,不过优势在于可以充分利用器件的资源和架构,减少客户的NRE成本。

发明时代的结束以FPGA的厂商大量减少而告终,摩尔定律引起的量变引起了FPGA技术的质变,FPGA进入了下一个时代。

扩张时代 1992-1999

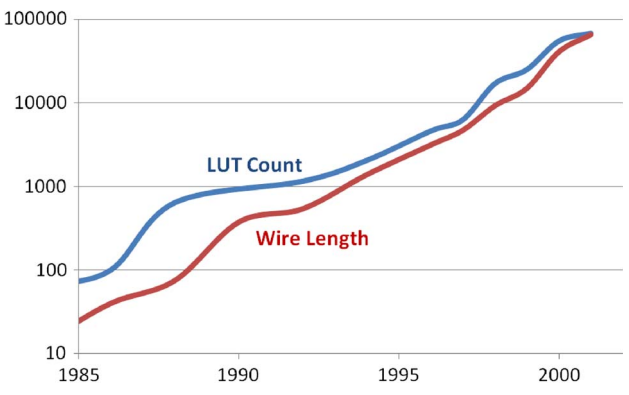

在1990年代,摩尔定律继续快速推进,FPGA初创公司在90年代初通常无法跟上最新的工艺,但之后代工厂一旦可以采用新的技术生产晶体管,就可以制造基于SRAM的FPGA。如下图所示,在90年代FPGA和LUT和Wire的数量以指数级增长,这种增长带来了很多影响。

面积不再那么重要

在1980年代,晶体管利用效率非常重要,但是到了1990年代,尽管面积仍然很重要,但是可以用来换取性能、功能和易用性。

EDA变得必不可少

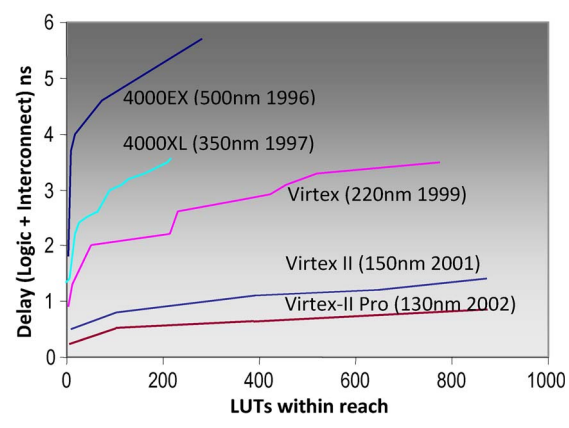

在这一时代,FPGA上的设计已经无法手动布局布线了,在1992年,Xilinx XC4010上最多可以有10000个门,但到了1999年,Virtex XCV1000上已经有一百万个门了,FPGA公司的生存逐渐取决于EDA工具的能力。与此同时,工艺进步导致布线资源增加,自动布局工具可以完成不太精确地布局。自动化的设计工具需要自动化友好的架构,即具有丰富的互联资源的架构,简化算法的决策。更丰富的布线资源也允许了跨越多个逻辑块的互连线的出现,使物理上距离较远的逻辑在逻辑上也可以更接近,提高性能。下图显示了工艺技术进步和互联范围提升带来的巨大性能提升。

不过不利的一面是,当不使用线的整个长度时,一部分布线资源被浪费了。类似的问题也出现在逻辑块的设计上,比如当设计三输入的逻辑时,四输入LUT中一半的配置单元就被浪费了。设计人员可以手动设计复杂的逻辑结构,但是自动化工具并没有那么聪明,且对于更复杂的设计,逻辑块的互联也变得更复杂。在这一时代,FPGA的幸存者是那些充分利用工艺进步并实现设计自动化的公司。

SRAM成为首选技术

EPROM、闪存、反熔丝等非易失性可编程技术通常无法跟上最新的工艺,但SRAM可以。反熔丝设备在特定技术节点上更高效,但是在新节点上进行验证需要几个月甚至几年时间,此时下一代的SRAM FPGA已经开始交付了。反熔丝的另一个缺点是缺乏可重复编程性,像ASIC一样需要有验证阶段,抵消了FPGA的优势。

LUT成为首选的逻辑单元

LUT架构很容易进行综合,尽管传统的ASIC综合器在基于LUT的FPGA上表现不佳,但是可以利用LUT能实现任意函数的特性来进行综合。LUT还提升了互联的效率,FPGA上的互联不是ASIC上的简单金属线,而是包含了缓冲器、路由器、负责控制的存储单元等一系列器件,由于LUT可以实现任何形式的函数,EDA工具只需要在LUT上所需的信号进行路由,输入可以任意互换,基于LUT的逻辑可以减少实现功能所需的互联数量,未使用的LUT功能所造成的浪费可以少于互联需求减少所节省的资源。

回顾

FPGA容量跟随摩尔定律而增长,引出了对设计自动化的需求,SRAM器件引领了新工艺技术的应用。FPGA设备容量的增长速度逐渐超过许多应用程序的需求,FPGA开始占领低端ASIC的领域。同时,FPGA供应商也始终保持自己对EDA工具的控制,如果依赖外部EDA工具,可能会导致FPGA的NRE成本变高,破坏FPGA的成本优势。

积累时代 2000-2007

FPGA已逐渐成为数字系统的常见组件,随着容量和设计规模不断增长,FPGA在数据通信行业发现了巨大的市场。2000年代初期的互联网泡沫破灭产生了对降低成本的需求,ASIC制造成本和复杂性让希望定制芯片的小团队望而却步,这些团队也就成为了FPGA的用户。这一阶段FPGA的规模也随着摩尔定律不断变大,但是客户并不一定愿意为过大的FPGA支付高额的溢价。仅增加产能也不足以保证市场增长,当FPGA容量超过一定程度之后,容量的增加带来的应用程序数量的增加程度逐渐减少,也就是说需要用到这么大容量的应用程序也不是很多了,也不再能吸引到越来越多的新客户。

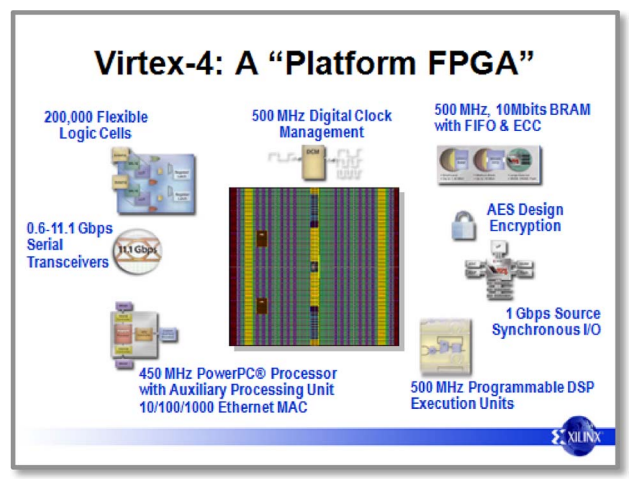

FPGA供应商以两种方式应对这一挑战。对于低端市场,他们重新关注效率并生产出容量较低、性能较低的“低成本”FPGA系列:Xilinx的Spartan、Altera的Cyclone和Lattice的EC/ECP。对于高端产品,FPGA供应商希望让客户更容易填满大容量的FPGA,为重要功能设计了软逻辑(IP)库,这些IP包括微处理器(Xilinx MicroBlaze、Altera Nios)、内存控制器和各种通信协议栈。在Virtex-4以硬件实现Ethernet MAC IP之前,这个功能是在LUT中作为Virtex-II的软核实现的。IP组件的标准接口消耗了额外的LUT,但与节省的设计工作量相比,这种低效率并不是一个大问题。

从2000年代开始,FPGA用户不再是单纯地实现逻辑,而是把FPGA作为大型系统的一部分,FPGA设计需要符合系统标准,可以和外部组件进行通信。遵守标准、降低成本和降低功耗的压力导致设计策略从简单地添加可编程逻辑、遵循摩尔定律增大容量(如扩展时代)转变为添加专用逻辑块,通常包括存储器、微处理器、乘法器、I/O等,可以减少面积、功耗以及设计工作方面的开销。

为了减轻使用新功能的负担并满足系统标准,FPGA供应商提供了逻辑生成器,为软核和硬核处理器上的外围设备提供CoreConnect、AXI和其他总线的接口。为了简化微处理器系统的创建,Xilinx提供了嵌入式设计套件(EDK),Altera也发布了嵌入式系统设计套件(ESDK),可以在FPGA处理器上运行Linux,并在FPGA架构中进行视频压缩和解压缩。但是对于那些不需要固定功能的客户,这些处理器、存储器或乘法器的面积就被浪费了。FPGA供应商一开始尝试利用这些面积,例如Xilinx可以将状态机映射到微处理器的代码中,但这些措施最终被认为并不重要,FPGA供应商和客户都接受了这种形式的浪费。

应用程序

这一时代FPGA最大的变化是目标应用程序的变化,FPGA业务的增长并非来自通用ASIC替代品,而是来自通信基础设施的采用。Cisco Systems等公司使用FPGA设计自定义数据路径,以通过其交换机和路由器控制大量互联网和语音流量,新的网络路由架构和算法可以在FPGA中快速实现并在现场进行更新,通信行业部门的销售额迅速增长,占FPGA业务销售总额的一半以上。这一成功促使主要的FPGA制造商为通信行业定制FPGA,专为通信而设计的FPGA包含高速I/O、数千个专用高性能乘法器等。为更好地满足通信应用要求而添加的专用块和路由减少了可用的通用逻辑区域。多核处理器和通用图形处理器单元(GPGPU)开始成为主流,但FPGA仍然是高吞吐量、实时计算的首选,且仍然保持了其通用性。

摩尔定律

在这个阶段,FPGA技术仍人在容量和成本方面继续改进,但功率也继续提高,性能的提升已经需要进行权衡,需要考虑低功耗的问题,在本文的第一张图中可以看到2000年代性能增长的放缓。这种权衡也推动了FPGA功能的积累,仅仅依靠工艺技术进步不足以满足功耗和性能的要求,需要在其他方面进一步做出改进。

当前时代:不再是可编程逻辑

在积累时代结束时,FPGA仍然是可编程的,但不再局限于可编程。FPGA与ASIC相比仍然有很多优势,但是与多核处理器和GPU相比,仍然有劣势。FPGA开发人员的压力也持续增加,2008年开始的经济增长放缓继续推动降低成本的需求,不仅表现在对降低功能价格的需求上,也表现在降低功耗上。

应用程序

随着工艺进步,ASIC NRE的成本越来越高,下图中的纵轴是以百万美元为单位的。前文中提到ASIC与FPGA成本的交叉点,已经增长到了几百万台,销售量如此之大的芯片很少,可能仅限CPU、存储器等,再加上对成本的要求以及销售的不确定性,可编程逻辑成为的首选的芯片解决方案。

ASIC也在不断扩展,通过片上系统(SoC)设备的形式增加可编程性。随着ASIC向SoC迁移,FPGA供应商开发了可编程SoC,即完全可编程的片上系统,包括存储器、处理器、模拟信号接口、片上网络和可编程逻辑块。Xilinx All-Programmable Zynq、Altera SoC FPGA和Actel/Microsemi M1就是这种新型FPGA的例子。

设计工具

这些新的FPGA具有新的设计要求。最重要的是,它们是软件可编程的以及硬件可编程的。微处理器不是像积累时代那样被放入FPGA中的简单硬件块,而是包括一个包含高速缓存、总线、片上网络和外围设备的完整环境。捆绑软件包括操作系统、编译器和中间件——一个完整的生态系统,而不是一个集成的功能块,编程软件和硬件一起增加了设计的复杂性。

工艺技术

尽管在过去的30年中工艺规模一直在稳步增长,但摩尔定律对FPGA架构的影响在不同时期却大相径庭。为了在发明时代取得成功,FPGA需要积极的架构和工艺创新。在扩张时代,紧紧跟随摩尔定律是增长市场份额最有效的方式。随着FPGA成长为系统中的重要组件,FPGA需要满足系统标准,并且是以低成本提供系统接口,FPGA行业依靠工艺技术扩展来满足许多系统要求。然而,工艺技术改进速度放慢,要求FPGA提出新型的电路和架构,且不能降低FPGA的易用性,为FPGA电路和应用工程师带来了更大的挑战。