原文:CONNECT: Re-Examining Conventional Wisdom for Designing NoCs in the Context of FPGAs.

CONNECT是一个NoC生成器,面向FPGA生成任意多节点拓扑结构的可综合RTL设计,这里有一个online demo。CONNECT的意义在于,传统的NoC设计都为ASIC优化,但是面向FPGA的NoC设计需要考虑到以下几点:

相比逻辑和存储资源相比,FPGA的导线资源相对丰富。

大量中等大小的缓冲区形式的片上存储资源较少。

深度流水线的性能回报较少。

极其灵活的应用特定的现场可重构性。

CONNECT NoC架构体现了一套以FPGA为动力的设计原则,这些原则独特地影响了关键的NoC设计决策,如拓扑结构、链路宽度、路由器流水线深度、网络缓冲区大小和流量控制。

适应FPGA的要求

布线资源丰富

FPGA的布线资源非擦和功能丰富,特别是相对于其他资源而言。传统NoC设计中,路由器通常被视为内部密集连接的组件,通过狭窄的通道相互连接,并复用大量信息。相反,FPGA的NoC应该是尽可能使通道尽可能宽,流量控制机制也可以使用更宽的接口,间接减少路由器的存储需求,CONNECT NoC架构还允许一个路由器的逻辑直接进入另一个路由器,以更有效地实现缓冲区的流量控制。

存储资源不足

FPGA提供BRAM和Distributed RAM两种存储形式,大部分可用的存储容量都以BRAM提供,且不能被进一步细分。对NoC来说,大量的缓冲区的容量通常逗比Distributed RAM大得多,但是又比BRAM容量小得多。因此,为FPGA调整的NoC应该对增加缓冲区大小的优化有较高的门槛,具体来说,CONNECT NoC架构完全避免使用BRAM,而是将Distributed RAM用于其数据包缓冲区,且缓冲区大小和配置考虑到了Distributed RAM的具体尺寸和大小,以更有效地利用LUT资源。

低时钟频率

时钟频率也是FPGA和ASIC最重要的差异之一,因而在FPGA上设计深度流水线以提高频率的回报很差。然而,FPGA在低频率下的性能损失可以通过增加数据通路和链路宽度来有效弥补,且CONNECT NoC架构中的浅流水线具有降低网络延迟的额外好处,并大大减少了路由器消耗的flip-flop数量。

可重构性

鉴于FPGA的灵活性,一个有效的NoC设计有可能被要求与各种不同的应用相匹配,因此也可以适配于一些特定应用。具体来说,CONNECT NoC架构并不是一个单一的IP,而是一个RTL设计生成器,可以生成专门适应一些应用的NoC实例,甚至是特定的逐次运行的工作负载。CONNECT NoC生成器完全是参数化的,网络遵循相同的简单标准通用接口。

CONNECT NoC架构

CONNECT NoC旨在成为更大的基于FPGA系统的一部分,因此CONNECT NoC需要在两个相互冲突的目标之间取得平衡:提供足够的网络性能和尽量减少FPGA上资源的使用。基于这样的设计理念,CONNECT和传统NoC的设计完全不同,具体有以下两点:

单级流水线:和大多数典型的3-5级流水线相比,CONNECT采用了单级流水线(就是没有流水线?),降低了硬件成本且减少了延迟,有机会实现更简单的流量控制和更高效的缓冲期使用。

紧密耦合的路由器:CONNECT在路由器中尝试使用更宽的接口来最大化布线资源的使用,导致耦合更紧密,包括在额外的线路上携带flit控制信息(而非在传统的设计中使用单独的header flit),这也允许路由器直接查看下游接受路由器的缓冲区占用信息。

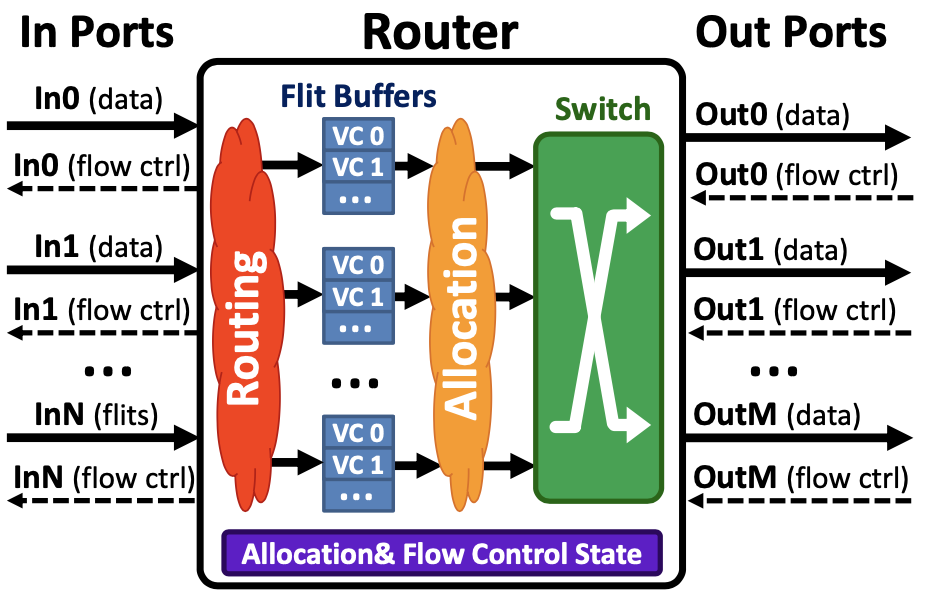

CONNECT路由器架构

路由器设计采用Bluespec System Verilog实现,保持灵活的可参数化设计,支持

- Variable number of input and output ports

- Variable number of virtual channels (VCs)

- Variable flit width

- Variable flit buffer depth

- Two flow control mechanisms

- Flexible user-specified routing

- Four allocation algorithms

数据包路由:路由是由查找表实现的,为网络中的每个可能目的地提供输出端口,这样的设计提供了灵活性,尽管对于大型网络可能需要大量条目,但CONNECT通过利用Distributed RAM以一种有效的方式来实现,占用的LUT数量通常少于10。

Flit缓冲区:Flit缓冲区是按输入组织的,通过在每个单读单写的Distributed RAM实现多个逻辑FIFO(每个VC一个FIFO)来实现缓冲区的设计。

缓冲区分配:CONNECT支持4中分离式输入-输出分配算法,分配模块由两个子模块组成,分别负责输入和输出的仲裁,产生符合条件的输入和可用输出的有效匹配。

设计特点

拓扑结构不可知:支持任意拓扑结构,且连接相同数量终端的CONNECT网络是可以互换的。

虚拟通道:支持多个VC,确保无死锁,也可以通过减少队列头部阻塞的影响来提高网络性能。

虚拟链接:当启用这个功能时,NoC保证多bit数据包的连续传输,保证了一旦一个数据包开始传送,就会在其他数据包传送之前完成,可能会轻微增加硬件成本,但是可以大大减少接收端的重组缓冲和逻辑设计要求。

Peek流量控制:可以很随意地翻译成“偷看”流量控制,传统的基于信用的流量控制通常被设计为可以容忍由于多周期链路延迟和路由器深流水线设计造成的长延迟,且支持在同一组线路上复用不同VC的流量控制信息以减少线路数量。在Peek流量控制中,路由器直接将缓冲区占用信息暴露给上游路由器,目前CONNECT使用单bit的peek流量控制,很类似于开关信号流量控制。