知乎原回答:https://www.zhihu.com/question/468593551/answer/2996304673

差不多正好两年前开始接触体系结构这个领域,通过一生一芯第一期项目和rocket-chip了解到了chisel这个语言,在2021年下半年参加了一生一芯第三期,也许也算是有资格来回答这个问题吧w,chisel的优缺点楼上各位大佬已经讨论的非常充分了,或许我会更多从自己项目经历和主观体验的角度,作为chisel语言的用户来聊一聊,希望各位大佬前辈多多批评。

首先放上自己一生一芯第三期的项目链接:https://github.com/OSCPU-Zhoushan/Zhoushan

我自己的背景是从大二的数电课开始接触verilog,本科毕设做处理器设计的时候有考虑过用chisel,和队友讨论下来还是不要选这些稀奇古怪的新语言了。不过后来8月中旬开始一生一芯第三期之后,还是没忍住诱惑,花了几天的时间快速入门了一下chisel,大概两三天的时间就写出了一个基本的五级流水线,最后10月初提交的版本是一个RV64I的乱序流水线。

Chisel本身作为一个HDL generator似乎很容易引起一些误解。首先chisel本身仍然是HDL,不是HLS,仍然需要很清楚地描述每一个wire和每一个register,因此有verilog背景的同学上手chisel是很快的(唯一的障碍可能是scala语言本身),我自己也非常不推荐cs的同学把chisel作为自己的第一个HDL语言去学。用chisel做IC开发本身的流程也和传统的流程没任何区别,仅仅是在RTL设计这一步换了个语言而已,就像写OS写数据库,并不会因为我把C换成rust,我就立马功力大增,写出了性能很好非常可靠的软件一样。

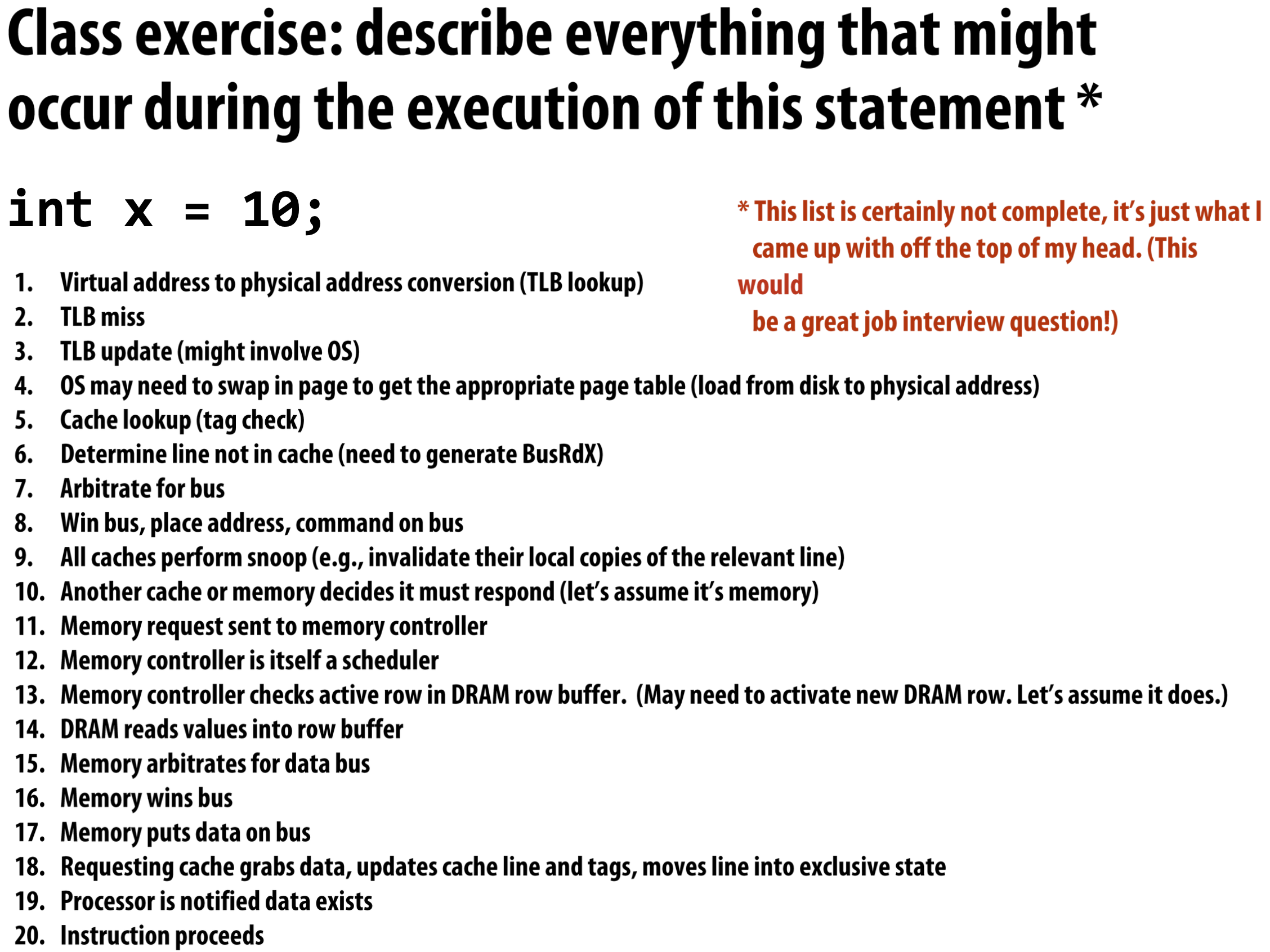

题外话:题主以及很多参加一生一芯的同学会觉得这个项目里cs背景的人更多也是很合理的,项目本身并不单纯是写写verilog、设计一个处理器就结束了,还包括了很多其他方面的学习,比如当我在程序里写下int x = 10这一句话的时候,实际上到底发生了什么事情,完整学习完一生一芯之后应该可以很从容回答这个问题了。(这个例子出自CMU 15-418 Parallel Computer Architecture & Programming)

出自 CMU 15-418 Spring 2023 Lecture 12 Snooping-based multi-processor implementation

出自 CMU 15-418 Spring 2023 Lecture 12 Snooping-based multi-processor implementation

我自己在写chisel的时候,初印象还不错,有时候会想HDL早就该这么设计了。一开始觉得不用像verilog那样手动连线了当然很爽,然后马上也会发现,因为是基于scala的一个DSL,scala的好东西chisel也都有,比如各种面向对象、类型推断、函数式编程之类的特性。比如ICache和DCache的接口可能非常相近,但还是有点差别,完全可以通过面向对象的特性来简化代码,提高可读性。

一生一芯结束之后,后续的一些RTL项目我基本都选择用chisel开发,还有很多用上了就回不去了的东西,比如chisel的高度参数化和很多好用的IP。在一生一芯项目期间我基本还只是把chisel当成了一个比较好写的HDL来使用,后面进一步了解之后发现rocket-chip本身就是个宝藏项目,比如有了diplomacy之后,不再需要去考虑手动计算某个总线的地址宽度应该是多少,或者某个crossbar应该怎么去连之类的问题,这些确实是verilog本身暂时做不到的事情。如果是做RISC-V处理器或者基于TileLink/AXI4总线的IP开发的话,rocket-chip和chipyard还有非常多好用的IP可以直接拿来用(https://chipyard.readthedocs.io/en/stable/TileLink-Diplomacy-Reference/index.html)。可以说确实在SoC集成的工作上chisel能节省不少工作量。

我和同学在聊到这个语言的时候偶尔会拿来和rust比较,但是个人看来chisel在HDL领域似乎远没有rust在编程语言领域那样成功,并且虽然自己非常喜欢这个语言,但是显然很长一段时间内chisel/firrtl这一套语言还不太会在工业界大规模应用。

首先chisel毕竟还是个和verilog站在同一层次的语言,大家确实没有很强的动力把verilog换成chisel,有的事情chisel做起来和verilog同样麻烦,比如跨时钟域,比如异步复位(似乎目前还没有一个选项可以调同步或异步复位?)。

其次chisel这个语言本身目前还在快速迭代,很多chisel 3.4还跑的好好的代码,到了3.5就说马上要deprecate了,原来0 warning的代码,更新了个版本马上几百个warning,说不准下次再更新一次chisel版本就变error了,很担心现在很多开源IP在10年之后还能不能顺利集成到那会的项目里面去。

提到开源IP,也真的非常想吐槽一下rocket-chip、boom、香山以及各种各样的开源项目,似乎都有这样的问题(也可能仅仅是我觉得这样做有问题…)。虽然很多chisel的语言特性用上确实很不错,但也能看得出来有些地方单纯是在炫技,比如明明可以用for循环用三四行实现的代码,一定要用函数式的写法在一行里写完,不只是降低可读性,还很难看出来哪根线连到哪。

顺着这一点继续说,chisel本身生成的verilog可读性就比较差,因为上述提到的各种新特性,生成的verilog几乎不可控,之后想debug做验证反而要花更多时间。以前verilog可能是有bug去看波形,找到代码的位置,改代码,现在是有bug先去看chisel代码,对着chisel代码找到verilog里的代码,找不到的话有时候还要加上dontTouch或者改写chisel代码,重新编译重新仿真,基本用chisel在RTL开发上省下来的时间全都在验证上找补回来了。

最后回到主题,问chisel会不会影响verilog工程师,有点像是问rust会不会影响C++工程师,我一直觉得使用什么语言只能决定一个工程师的水平下限,就好比rust编译器可以保证一个人不会写出内存泄漏满天飞的代码,chisel可以保证不会写出带latch的数字电路一样,但是决定一个人水平上限仍然还有很多其他东西。